# Survey of Energy-Cognizant Scheduling Techniques

Sergey Zhuravlev, Juan Carlos Saez, Sergey Blagodurov, Alexandra Fedorova and Manuel Prieto

Abstract—Execution time is no longer the only metric by which computational systems are judged. In fact explicitly sacrificing raw performance in exchange for energy savings is becoming a common trend in environments ranging from large server farms attempting to minimize cooling costs to mobile devices trying to prolong battery life. Hardware designers, well aware of these trends, include capabilities like DVFS (to throttle core frequency) into almost all modern systems. However, hardware capabilities on their own are insufficient and must be paired with other logic to decide if, when, and by how much to apply energy-minimizing techniques while still meeting performance goals. One obvious choice is to place this logic into the OS scheduler. This choice is particularly attractive due to the relative simplicity, low cost, and low risk associated with modifying only the scheduler part of the OS. Herein we survey the vast field of research on energy-cognizant schedulers. We discuss scheduling techniques to perform energy-efficient computation. We further explore how the energy-cognizant scheduler's role has been extended beyond simple energy minimization to also include related issues like the avoidance of negative thermal effects as well as addressing asymmetric multicore architectures.

Index Terms—Survey, Shared Resource Contention, Thread Level Scheduling, Power-aware Scheduling, Thermal Effects, Asymmetric Multicore Processors, Cooperative Resource Sharing.

## **1** INTRODUCTION

Increasingly widespread use of computer systems and rising electricity prices have brought energy efficiency to the forefront of the current research agenda. Energy consumption has become a key metric for evaluating how good a computer system is, alongside more traditional performance metrics like the speed of execution. A lot of effort is focused on building more energyefficient devices, but even as the hardware becomes more energy efficient, the onus of extracting the maximum efficiency out of it very often falls on the software. This is particularly true about the CPU devices, which consume nearly half of energy in server systems. Modern processors provide "knobs" allowing to trade execution speed for power efficiency, but the decision of how to use these knobs to minimize the impact on speed while saving as much energy as possible falls onto the runtime resource manager, such as the operating system. Tuning the settings of energy-management knobs often involves deciding when and where to run each software thread and at what speed - these decisions are natural to make as part of conventional process scheduling routines. Therefore, we refer to CPU energy-management policies and algorithms employed in the software runtime as energy-cognizant scheduling. Energy-cognizant scheduling is the subject of this survey, and we focus specifically of managing energy consumption of the CPU.

We examine three types of hardware mechanisms allowing us to manage CPU energy consumption: (1)

Dynamic Voltage and Frequency Scaling (DVFS) and Dynamic Power Management (DPM), (2) thermal management and (3) asymmetric multicore designs.

1

DVFS and DPM allow us to dynamically throttle the voltage and frequency of the CPU or to temporarily suspend its operation and put it in a low-power state. As we throttle or suspend the processor we inevitably sacrifice execution speed, and so the key challenge in designing DVFS/DPM control algorithms is to find the setting that saves the most power while sacrificing the least speed. This requires understanding applications' characteristics and the intricacies of their interaction with the hardware, and that is why DVFS/DPM control algorithms are non-trivial to design and are undeniably interesting.

We then survey runtime algorithms that perform thermal management. Although in a somewhat indirect fashion, processor temperature plays a crucial role in energy consumption, because as the temperature becomes high, the system needs to run fans to cool off the processor. Cooling consumes electricity, and so managing system temperature can reduce the amount of energy spent on cooling. Thermal management relies primarily on altering the physical placement of threads on cores so as to avoid thermal hotspots and temperature gradients (when one area on the chip is much hotter than another). Thermal management algorithms rely on curious and unexpected effects on processor temperature created by the instruction mix, the physical placement of threads on the chip and threads' relative proximity to one another.

While DVFS and DPM allow dynamically throttling the speed and thus the power consumption of the processor, even greater energy efficiency can be achieved if CPU cores are engineered from the start to be low-

S. Zhuravlev, S. Blagodurov and A. Fedorova are with the SyNAR Group, School of Computing Science, Simon Fraser University, Burnaby, B.C. V5A 1S6, Canada

J.C. Saez and M. Prieto are with the ArTeCS Group, Complutense University of Madrid, Madrid 28040, Spain.

2

power. However, low-power cores typically offer smaller and weaker execution engines than their high-power counterparts, making significant sacrifices in processing speed . An interesting attempt at resolving this dilemma is offered by *asymmetric* systems. These systems are built with both low-power and high-power cores on the same chip. Both core types are able to execute the same binary, but they differ in microarchitecture, power profiles and performance<sup>1</sup>. As a result, the thread scheduler can use this asymmetry as a knob for controlling speed-energy trade-off. By scheduling threads that do not benefit from advanced features of high-power cores on lowpower cores and vice versa, the scheduler can maximize performance within the system's frugal power budget.

While the algorithms discussed in this paper were developed for different types of energy-management mechanisms their unifying theme is that they work by dynamically monitoring properties of the workload, making decisions that consider how the characteristics of the workload interplay with those of the hardware, and controlling the configuration and allocation of CPU cores so as to make the best trade-off between performance and power consumption.

This survey is organized as follows. Section 2 introduces basic concepts on power and energy consumption and presents a classification of the different techniques analyzed in this survey. Section 3 covers scheduling algorithms that use DVFS and DPM. Section 4 discusses thermal management. Section 5 focuses on scheduling for asymmetric machines. We conclude and discuss what we see as the future directions of energy-cognizant scheduling research in Section 6.

## 2 BACKGROUND

## 2.1 Power dissipation basics

CMOS devices are the building blocks of most generalpurpose computing systems today. Power consumed in CMOS circuits can be divided into three components: *dynamic, static* and *short-circuit* power. For many years *dynamic power dissipation*, which occurs due to the switching of transistors, has been the dominant factor in CMOS power consumption. Dynamic power can be approximated with the following formula:

$$P_d = C_l \cdot N_{sw} \cdot V_{dd}^2 \cdot f \tag{1}$$

where  $C_l$  is the load capacitance, a significant percentage of which is wire related,  $N_{sw}$  is the average number of circuit switches per clock cycle,  $V_{dd}$  is the supply voltage and f is the clock frequency.

The shrinking of the feature size in the latest technology generations has enabled to substantially reduce the supply voltage ( $V_{dd}$ ), which reduces power dissipation quadratically. Unfortunately, decreasing the supply voltage increases the circuit delay and so the circuits

1. Heterogeneous systems where cores of different types support different instruction sets are not discussed in this survey.

cannot be driven at the same clock frequency. More specifically, the clock frequency is almost linearly related to the supply voltage as follows:

$$f = k \cdot \frac{(V_{dd} - V_{th})^2}{V_{dd}} \tag{2}$$

where k is a constant and  $V_{th}$  is the threshold voltage [1], [2]. In turn,  $P_d$  is roughly cubically related to  $f: P_d \approx C_l \cdot N_{sw} \cdot \frac{f^3}{k^2}$ . As a result, a reduction in the supply voltage and the clock frequency reduces dynamic power cubically (and dynamic energy quadratically) at the expense of up to a linear increase of execution time. For example, consider an application that takes 10 seconds to complete at a given processor frequency f. At this frequency the dynamic power and energy of the task is denoted by  $P_d$  and  $E_d$  respectively, where  $E_d = P_d \cdot \text{completion\_time}$  (hence,  $E_d = P_d \cdot 10$ ). Suppose further that, when reducing the processor frequency and supply voltage by half, this task takes 20 seconds to complete. The new dynamic power  $P'_d$  and energy  $E'_d$ consumed by the task in this scenario would be:

$$P'_{d} = C_{l} \cdot N_{sw} \cdot \left(\frac{V_{dd}}{2}\right)^{2} \cdot \frac{f}{2}$$

$$= \frac{1}{8} \cdot C_{l} \cdot N_{sw} \cdot V_{dd}^{2} \cdot f = \frac{1}{8} \cdot P_{d}$$

$$E'_{d} = P'_{d} \cdot 20 = \frac{5}{2} \cdot P_{d} = \frac{5}{2} \cdot \frac{E_{d}}{10} = \frac{1}{4} \cdot E_{d}$$

The second component of power dissipation, static (or leakage) power, has to do with the existence of leakage current flowing between the power source and the ground. Subthreshold leakage, the main subcomponent of leakage power, represents the power dissipated by a transistor whose gate is intended to be off. In the latest process generations subthreshold leakage power has increased exponentially with respect to previous generations, mainly due to joint reductions in the supply and the threshold voltage<sup>2</sup>. Currently, leakage power constitutes 20–40% of the total power dissipation [3]. Of special attention is the exponential dependence of leakage power on temperature. As the system's temperature rises, leakage power becomes a more significant portion of the total power. Most research efforts to reduce leakage power consumption are taking place at the process level [4], [5] and at the microarchitectural level [6], [7], [8], and so they are not not within the scope of our survey. Nevertheless due to the relation between temperature and static power, techniques described in Section 4, which strive to control the processor temperature, contribute to reducing static power as well.

Finally, short-circuit or "glitching" power is the power dissipated when both the n and p transistors of a CMOS gate are conducting simultaneously. Because

<sup>2.</sup> It is evident from Equations 1 and 2 that  $V_{dd}$  and  $V_{th}$  have to be scaled down simultaneously in order to maintain performance while saving power.

short-circuit power is comparatively insignificant to dynamic and static power, this component of power consumption has not drawn as much attention as the others from the research community and the industry.

#### 2.2 Energy Management at Runtime

Examining the relationships in Eq. 1 justifies three main research directions aiming to reduce system energy consumption via software techniques used at runtime. The first group of solutions is based on **Dynamic Voltage and Frequency Scaling (DVFS) and Dynamic Power Management (DPM)**. These solutions dynamically vary the processor voltage and frequency. Since reducing voltage and frequency may lower performance, the DVFS/DPM based solutions consider relationship between frequency and performance, taking into account the fact that some applications slow down less than others when processor frequency is reduced.

The second group of solutions, **Thermal Management**, has to do with the fact that processor temperature has a significant impact on energy consumption. For example, when a processor heats up, the system must increase activity of the cooling infrastructure (e.g., fans), which consume energy. This group of solutions relies on the observation that different applications have different effect on processor temperature and leverages interesting spatial dependencies when it comes to temperature control. For instance, running two heat-generating threads on adjacent cores will create a greater thermal gradient than running these threads on separate parts of the chip. Thermal management algorithms thus perform spatial and temporal placement of threads so as to minimize thermal emergencies and to reduce thermal gradients, which occur when the variation in temperature on different parts of the chip is high.

The third group of solutions, Asymmetry-Aware Scheduling, has to do with systems that are *asymmet*ric in nature. Fundamentally, the system's power consumption depends on its microarchitecture: for instance, systems clocked at higher frequencies and featuring more complex pipelines and larger caches consume more power than smaller processors with simpler features. However, simpler and smaller processors also offer lower performance. To resolve the energy-performance trade-off, some researchers proposed to build systems that include both complex, fast and power-hungry cores as well as simple, lean and power-efficient cores. These systems are called asymmetric. In this survey we for the most part discuss symmetric-ISA (Instruction Set Architecture) asymmetric-performance systems –where all cores can run the same application binary, but offer different performance.

In symmetric-ISA asymmetric-performance systems the onus of deciding which type of core should be used to run a particular thread falls on the operating system scheduler. Intelligent scheduling algorithms that optimize system energy and performance are thus crucial. Another category of asymmetric systems is where asymmetry is not an explicit design feature, but occurs because of routine hardware faults (e.g., cores that were meant to run at identical frequencies actually run at different ones). These systems share similar challenges as explicitly asymmetric systems. However, because of the dynamic nature of their asymmetry (e.g., hardware faults making the system asymmetric can occur anytime during the execution) we logically place these solutions in the same category as DPM and DVFS.

To summarize, energy-management optimizations in the thread scheduler can be classified in three categories according to the mechanism upon which they rely: (1) Dynamic Power Management and Dynamic Voltage/Frequency Scaling, (2) Thermal Management, and (3) Asymmetry-Aware Scheduling. Table 1 summarizes the main challenges addressed by the these solutions as well as key ideas behind them. Detailed discussion of these techniques is presented in the rest of the paper, in Sections 3, 4 and 5 respectively.

## 3 DYNAMIC VOLTAGE/FREQUENCY SCALING AND DYNAMIC POWER MANAGEMENT

#### 3.1 Basics of DPM and DVFS

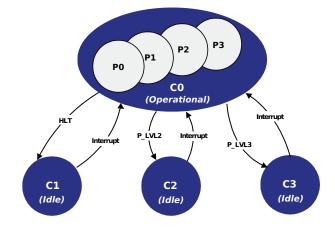

Dynamic Power Management (DPM) exploits the fact that certain electronic components/devices may remain idle a significant amount of time and so they could be turned off during inactive periods to save energy. Hardware and software manufacturers have agreed to create standards such as the ACPI (Advanced Configuration and Power Interface) [9] with introduces several modes of operation enabling to turn off some parts of the system such as processor cores, hard drives or Ethernet cards. Contemporary devices offer different power states. As an illustrative example, Figure 1 depicts the different power states for processors implementing the ACPI specification. The idea behind DPM is that these devices periodically enter idle periods where no work is available and as a result can be brought into a less energy-hungry sleep state. The drawback is that when work becomes available the device needs to be brought back into the operational state, and this transition incurs additional latency. The lower the power state (higher number associated with it), the greater the energy savings; however the transition latency also becomes higher for lower active states.

While DPM brings components into non-operational but energy-efficient states, Dynamic Voltage and Frequency Scaling (DVFS) lowers the dynamic power used by the processor by limiting its clock frequency (f) and/or the supply voltage ( $V_{dd}$ ). As stated earlier, a joint reduction in f and  $V_{dd}$  enables to reduce dynamic power cubically and energy quadratically but may lead to an increased execution time.

| Technique                     | Goals                                                                                                                                                            | Key Ideas                                                                                                                                                                                                                                    | Approaches                                                                                                                                                                                                                          |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DVFS/DPM                      | Reduce operating volt-<br>age/frequency or power state<br>while minimizing or bounding<br>effect on performance.                                                 | Some applications suffer<br>less performance loss from<br>frequency reduction than<br>others. Real-time and deadline-<br>driven applications have<br>performance slack: no benefit<br>from performance gains past<br>meeting their deadline. | <ul> <li>Processor frequency is selected based on:</li> <li>1) a performance model for relationships between performance and power based on application characteristics;</li> <li>2) a static processor-specific model</li> </ul>   |

| Thermal<br>management         | Reduce thermal emergencies<br>and thermal gradients by pro-<br>actively or reactively moving<br>"guilty" threads away from<br>areas that are likely to overheat. | The type of computation that<br>threads execute affects how<br>much heat they are going to<br>generate.                                                                                                                                      | <ol> <li>Reactively move threads from hot to<br/>cool areas;</li> <li>pro-actively avoid clustering those<br/>threads that are more likely to pro-<br/>duce heat.</li> </ol>                                                        |

| Asymmetry-Aware<br>Scheduling | Assign threads to cores so per-<br>formance is maximized                                                                                                         | The relative benefit of running<br>on a "fast" vs. "slow" core<br>depends on the type of code<br>being executed: e.g., compute-<br>intensive vs. memory-intensive,<br>parallel vs. serial.                                                   | <ol> <li>Trial-and-error: schedule threads,<br/>measure performance, adjust;</li> <li>Analytical modeling: predict perfor-<br/>mance of a thread on a core type<br/>given threads characteristics mea-<br/>sured online.</li> </ol> |

TABLE 1 Summary of runtime power management techniques

Fig. 1. A processor can be either in an inactive very-lowpower (C1, C2, ..., Ck) state, or in an active state (C0) where it can execute instructions. In turn, for processors in the C0 state a performance/energy trade-off can be made via multiple performance (Px) states, typically characterized by different clock frequencies and supply voltages.

#### 3.2 Algorithms using DVFS and DPM

Weiser et al. [10] were the first to propose the use of DVFS to reduce the energy consumption in computing systems. They explored a set of OS-level scheduling algorithms to reduce CPU idle times by dynamically adjusting the DVFS level and evaluated each algorithm by means on simulated execution traces.

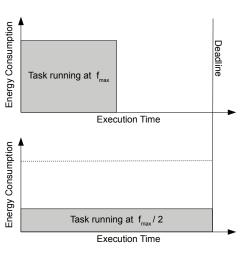

Early research efforts exploiting DVFS to reduce energy consumption arose in the context of real-time systems, where tasks' deadlines are given and their WCETs (*Worst-Case Execution Times*) are typically known beforehand. Many algorithms proposed in this domain have leveraged the *performance slack* available in real time applications [11], [12], [13], [14]. The common approach is to minimize energy consumption by reducing the performance of the processor (DVFS level) but without causing the applications in the workload to miss their deadlines (as depicted by Figure 2). This approach relies on the observation that completing an application before its deadline and then idling (e.g., via DPM), is less energy efficient than running the task at a lower clock speed and finishing it just in time. Yao et al. [11] propose an optimal static (off-line) scheduling algorithm for independent tasks. Another static scheduling algorithm is presented by Ishihara and Yasuura in [12] which relies on the fact that a task's average switch activity (the  $C_l \cdot N_{sw}$ factor in Equation 1) is known prior to the execution. Exploiting this additional information enables the proposed algorithm to reduce energy consumption by 70%. Aydin et al. [13] show that using exclusively WCETs to guarantee the temporal constraints of the workload, lack the potential to take advantage of the unused computation time since actual and worst-case execution times in real-time applications may differ significantly. Their experimental evaluation demonstrates that the proposed dynamic and speculative solutions, which exploit the unused computation time, achieve up to 50% energy reduction with respect to a static algorithm (based on WCETs). The two scheduling algorithms proposed by Zhu et al. [14] (designed for independent and dependent tasks respectively) aim to overcome the main limitation of previously proposed techniques [11], [12], [13]: they were specifically designed for uniprocessor systems. As Aydin's proposals [13] the scheduling algorithms presented in [14] also exploit the unused computation time to dynamically adjust the processor speed but are capable of sharing this *temporal slack* among processors.

4

Another early work utilizing DVFS for dynamic power management was from Isci et al [15]. Unlike more recent

Fig. 2. This figure shows two executions of a task running at different voltage and frequency (DVFS) levels. In the top graph, the task runs at full speed and finishes well in advance of its deadline. In the bottom graph, the processor frequency (and supply voltage) is reduced by half so that the task's deadline is just met, which leads to less energy consumption.

works in this area, they did not account for different effects of frequency scaling on different applications. Instead, they use a static estimate of power consumption and performance at each processor operating mode. They assume three operating modes: Turbo, where the processor runs at the highest available frequency and consumes most power, Eff1, where voltage and frequency are reduced by 5%, and corresponding power savings and performance loss are statically estimated at 14% and 5% respectively, and Eff2, with 15% voltage/frequency scaling, and 38% and 17% estimated power savings and performance loss. Their best power management policy, called MaxBIPS, simply chooses the mode that is expected to deliver the highest throughput (measured in Billions of Instructions per Second (BIPS)) given a power budget, based on the static estimate of power savings and performance loss in each mode. Although this simple policy delivered significant power savings, subsequent research attempted to take into account varying application characteristics when designing power management policies.

Most of the newer algorithms rely on the observation that different applications respond differently to changes in DVFS level, some suffering more performance loss than others. In particular, the work by Dhiman [16] as well as many others [17], [18], [19] illustrate that the degree of performance degradation that an application experiences as the processor frequency is lowered depends on how compute-bound the application is. Tasks that are completely compute-bound, referred to as *burn\_loop* [16], [20], show a linear dependence between processor frequency of execution time. Tasks that are completely memory-bound, referred to as *mem* [16], [20], show negligible slow-down as processor frequency is reduced. Finally, applications in-between the two extremes, termed *combo* [16], [20], have behavior in the middle. Memory-bound tasks suffer less from reduced CPU frequency, because the frequency of memory is not reduced. Choosing the right DVFS setting for combo applications is a delicate balance between reducing power consumption and increasing execution time.

5

Dhiman and Rosing [16] address this challenge by characterizing applications with respect to their degree of memory-boundedness. To do this online, they estimate each thread's *Cycles Per Instruction (CPI) stack* using hardware performance counters available on modern processors. CPI stack is a break-down of cycles spent executing instructions vs. stalling the processor on cache misses, TLB misses and memory accesses. Each thread is then characterized by the metric  $\mu$ , which is ratio of the cycles it spends on instruction execution to the overall cycles. A lower  $\mu$  indicates memory boundedness, and higher  $\mu$  (approaching 1) indicates CPU-boundedness.

The authors then dynamically choose between several voltage-frequency settings, which they deem *experts*, depending on the  $\mu$ -value prevalent for the currently executing workload. If the workload is predominantely CPU-bound an expert with a higher voltage-frequency value would be chosen and vice versa. The  $\mu$  for each task is continuously estimated to account for phase changes in programs. In relating the dynamically changing properties of currently executing workload to the system voltage-frequency setting, the authors achieve as much as 49% energy savings.

In [21], Lee and Zomaya exploit DVFS to devise energy conscious task scheduling algorithms for heterogeneous distributed systems (multiprocessor and multicomputer systems). This complementary study analyzes DVFS techniques in the context of precedence-constrained parallel applications. They focus on exploiting CPU idle time slots caused by intertask communications and are able to reduce energy consumption with little effect on the overall execution times.

In [20], Dhiman and Rosing build on their DVFSbased power management algorithm [16] and on their earlier work that used purely DPM [22]). For each task they employ the techniques of [16] to select the best DVFS policy. However, when the processor becomes idle they use an approach similar to their dynamic DVFS algorithm to so decide if/when to put a processor into a lower power state.

Work such as [15] implicitly raises an important question about the granularity of DVFS control in a CMP. Is it necessary, for performance-energy optimization, to provide a per-core frequency and voltage control knob? Doing so adds significant complexity to the manufacturing of the chip while on the other hand offers unparalleled performance optimization potential. Herbert and Marculescu [23] attempted to answer this question by simulating a CMP with different granularities of DVFS control, which they term *VF-Islands* (each island has a voltage-frequency knob associated with it; by varying the number of cores found in an island they vary the control granularity). Their experiments with different workloads and DVFS policies show that providing per core control will translate into minimal performance gains while dramatically increase scheduling complexity as compared to the control-granularity of several cores per VF-Island. This is also the dominant trend in modern architectures that place DVFS control at the granularity of a group of several cores<sup>3</sup>, most commonly the group of cores in the chip that share the last-level cache.

As mentioned earlier, DVFS is only capable to reduce the dynamic component of power consumption, which depends on f and  $V_{dd}$ . The increasing portion of static power in the total power dissipation of upcoming manufacturing technologies has led several researchers to exploring the real limits of using DVFS to reduce energy consumption today. Cho and Melhem [26], [27] derive analytical models to study the potential of DPM and DVFS to reduce energy consumption for parallelizable applications on multicore systems. In their analysis, they consider two different scenarios: one where just DVFS is supported and the other where both DPM and DVFS are available. The obtained models reveal that substantially greater power savings can be obtained in the second scenario where individual processors can be turned off. LeSueur and Heiser [28] take this observation one step further by illustrating that the energy savings benefits of DVFS are diminishing in recent processors due to rising static power consumption and reduced dynamic power range. Furthermore, their analysis suggests that in future generations turning-off unused processors (by setting these in ultra low-power states) will enable greater energy savings that using DVFS.

### 3.3 Mapping Execution to Physical Resources

The work discussed thus far in this section has treated all computational cores as being completely equivalent and as such has not addressed the issue of mapping execution to physical contexts. However, due to the facts that different cores can be throttled to different degrees creating an artificially asymmetric system, and because variations in manufacturing create homogeneous cores which are not all that homogeneous, mapping of execution contexts to physical resources becomes a vital part of energy-cognizant scheduling.

Teodorescu and Torrellas [29] discuss scheduling in light of the fact that due to variations in the manufacturing process even homogeneous cores of a CMP are in fact heterogeneous. More specifically, the cores vary in the amount of power that they consume and in the maximum frequency that they support [29]. Work that focuses on intentionally-manufacture asymmetric systems is discussed in Section 5. The authors of [29] explore algorithms that reduce power consumption in the presence of heterogeneity, such as first utilizing the least power-hungry cores, and mapping the most power-intensive threads to the least power-hungry cores. They also explore algorithms that improve performance in the presence of core frequency variation such as first utilizing cores that support the highest frequency or mapping high-IPC threads to high-frequency cores. Algorithms that optimize performance under the constraint of a power budget are explored as well. Having first mapped high-IPC threads to high-frequency cores they meet power budget constraints by applying DVFS to cores in a round-robin fashion, using a global linear optimization solution or simulated annealing.

6

Shin and Kim [30] consider the problem of constructing conditional task graphs for real-time applications, mapping the tasks to the available cores, and setting the DVFS for each core to just meet the timing deadlines while consuming the minimal amount of power. Freh et al. [31] propose a multithreading library that uses online performance counters as well as a sophisticated performance/energy prediction model to decide on the optimal number of threads to run as well as the number of threads to map to each core to optimize the energydelay product (EDP) for every phase of execution.

Kadayif et al. [32] take an interesting approach to the mapping / energy optimization problem. The authors make the observation that when the iterations of a nested loop are parallelized to be executed by multiple threads on multiple cores the amount of work that the different threads have to do can vary significantly. To demonstrate this issue consider a nested loop where the outer for loop iterates (1 < j < 1000) and the inner for loop iterates (j < k < 1000). Suppose this loop is divided between two threads such that all iterations with j < 500 are done by thread A and all other iterations are done by thread B. Because the inner loop is conditional on the value of j thread A has nearly twice as much work as thread B. In order to keep synchronization simple it would typically be the case that no further work will be scheduled until all the threads executing the same loop have finished. As a result, the core that executes thread B will be idle while thread A finishes. To compensate for this wasteful scenario the authors propose compile-time support that will estimate the workload assigned to each core (in a parallelization of nested loops scenario) and apply DVFS to the cores with less work assigned to them such that all threads will finish at roughly the same time. This makes each core consume the minimal energy possible to get its portion of the loop done, while keeping the execution time for the whole loop unchanged.

## 3.4 Integrating Contention Awareness into Energy/Power Solutions

As mentioned earlier, shared resource contention is a serious and well documented problem in chip multicore processors [33]. The issue stems from the fact

<sup>3.</sup> This is the case of cutting-edge Intel processors such as the Intel Core i7 [24] processor and the Single-chip Cloud Computer (SCC) [25]. An example of processor supporting core-level DVFS is the AMD Opteron "Barcelona" processor. This processor allows each core to operate at a different frequency, but the voltage must be no lower than that required by the core operating at the highest frequency.

that the cores of the CMP are not fully independent processors but rather share resources such as the Last Level Cache (LLC), prefetching hardware, the memory bus and DRAM memory controllers. Some researchers have measured that threads can slow down by hundreds of percent when competing for these resources with other threads on neighboring cores as compared to running alone on the machine. There has also been significant research effort on mitigating the negative effects of shared resource contention. Solutions ranging from hardware-based cache partitioning or DRAM scheduling to contention-aware OS thread schedulers have been explored. In this subsection we survey energy-cognizant scheduling solutions that take into account the negative effects of shared resource contention.

There have been three distinct branches of research on the issue of shared resource contention in CMPs in the context of power/energy scheduling. Kondo et al. [34] use DVFS to mitigate shared resource contention and provide fairness. Takagi et al. [35] and Watanabe et al. [36] show how combining contention-mitigation techniques with power/energy scheduling leads to better solutions. Dhiman et al. [37] show that using purely contention-mitigation techniques also significantly reduces energy consumption.

The work by Kondo et al. [34] addresses the problem of shared resource contention, in particular memory bus contention, affecting different threads differently and hence distorting fairness. The authors define a thread's performance degradation as the ratio of instructions per second (IPS) with contention versus the IPS without contention. They define the unfairness between two threads as the difference in the performance degradation of these two threads. With the goal of minimizing the unfairness between threads sharing resources they employ the energy/power minimizing technique of DVFS to throttle the core running the more aggressive thread. In the proposed scheme, on every cycle they record the number of outstanding cache misses for every core, as well as the IDs of the cores whose misses are being serviced in that cycle. Using this information, the authors calculate the number of cycles that each core (with the corresponding thread on it) has delayed every other core. If the delay value between two cores is larger than a predetermined threshold then the offending core is throttled (using DVFS) to lessen its ability to impede the progress of others. By raising and lowering the frequency-voltage settings for cores in response to biased usage of sharedresources the authors improve fairness in a CMP.

While Kondo et al. [34] use DVFS as a tool to improve fairness, Takagi et al. [35] and Watanabe et al. [36] argue that in order to use DVFS effectively as a power reduction technique on a CMP, shared resource contention must be first controlled by other means. If one of the threads gains greater access to the shared resources then it becomes necessary to compensate the other thread with a higher DVFS setting so that it still meets its performance deadlines. The power model derived in [36] reveals that the power consumption of the entire CMP is minimized if the frequency setting for every core is equal. In order to achieve this, the authors implement a priority control mechanism for access to the shared memory bus. Power optimization is then achieved by controlling both the priority of memory accesses of the cores as well as the corresponding DVFS levels. The work by Takagi [35] expands on [36] by also considering shared LLC contention. Along with priority control for the memory bus and setting DVFS such that the deadline is just met, [35] also partition the LLC among the competing threads based on stack distance profiles for these threads. Stack distance profiles are a compact summary of a thread's memory re-use pattern that can be used to predict the number of cache misses and therefore the expected performance of the thread with different amounts of cache space available to it. The downside of stack distance profiles is that, they cannot be obtained dynamically online for the majority of commercially available processors.

7

The work presented by Dhiman et al. [37] is highly correlated to work done on contention-aware CMP thread level schedulers. Studies such as [33], [38], [39], [40], [41], [42], [43], [44], [45] have used a myriad of different techniques to decide which thread-to-core mappings minimize shared resource contention. A common conclusion of these studies on contention-aware scheduling, was that a heterogeneous workload, one consisting of both compute- and memory-bound applications, is found to perform the best if different types of applications are paired together as opposed to when the same type of applications are paired together. Dhiman et al. achieve similar conclusions but stands out in that the stated goal of their work [37] was power/energy minimization. The biggest difference is that while the schemes presented in [33], [38], [39], [40], [41], [42], [43], [44], [45] separated applications in order to achieve higher performance, the algorithm proposed by Dhiman [37] does so to minimize power consumption. The other noteworthy difference is that Dhiman et al. [37] consider not individual applications being mapped to cores, as was done in all the contention-aware scheduling studies cited, but rather Virtual Machines (VMs) being mapped to Physical Machine (PMs). However, since the authors only execute one benchmark per VM and the benchmarks are from the same benchmark suites that were used by the majority of the contention-mitigation studies, the results are similar. The authors found that when memory-intensive applications (VMs) are executed on the same PM performance significantly degrades resulting in longer execution times, which translates into higher energy use. The finding that memory-intensive applications suffer performance degradations and prolonged run times matches the conclusions reached in [33], [38], [39], [40], [41], [42], [43], [44], [45]. Another notable observation is that PMs loaded with compute-bound VMs will draw significantly more power (since compute bound applications are more power-hungry) than PMs loaded with

memory-bound VMs leading to the undesirable effect of a power imbalance between the PMs. The authors of [37] propose a VM management utility called *vGreen* which schedules the VMs to the PMs in such a way as to balance the MPC (misses per cycle), IPC, and CPU-utilization across the PMs. Doing such balancing, which boils down to scheduling a heterogeneous mix of compute- and memory- bound VMs to each PM, resolves the power imbalance issue but more importantly reduces shared resource contention between the VMs facilitating a faster execution time and a reduced energy usage.

## 3.5 Summary

The manufacturers of modern processors are well aware of the need and desire to reduce power consumption of computing tasks as evidenced by the complex logic present ubiquitously on contemporary architectures to bring components into a low power state (DPM) or throttle processing power (DVFS). Ironically this logic, although available, often goes unused since hardware capabilities alone are insufficient and need to be paired with a decision mechanism which will determine when and by how much to invoke these features. The OS scheduler is a natural location to place such a decision mechanism as supported by the work surveyed in this section. The most obvious task that the scheduler must perform is to decide which components can be throttled and to what extent. One example is throttling cores running threads which are constantly blocked waiting on memory access. Such threads are prime candidates for throttling since they experience minimal slow downs at lower frequencies and hence offer pure energy savings. Complexity is encountered because the scheduler must be able to measure the memory usage characteristics of threads in order to apply this heuristic as well as deal with situations where threads are only partially memory-bound. Significant further complexity arises because cores, even in explicitly symmetric, systems are not necessarily homogeneous. Variations in the manufacturing process lead to cores with different powerdissipation properties and different maximum frequencies that they can support. This provides the energycognizant scheduler with the additional task of mapping contexts of execution to physical resources based on the properties of these physical resources on top of the original task of throttling the physical resources. Yet further complexity is added to the problem because of shared resource competition among threads scheduled to "neighboring" cores of a multicore processor. Shared resource contention can lead to significant performance losses which will directly translate into unnecessary energy expenditures. As such, a comprehensive energycognizant scheduler must be shared-resource aware and find a mapping of threads-to-cores as well as DVFS settings for these cores which minimizes shared-resource contention, accounts for the potential heterogeneity of cores, and satisfies some energy-performance metric.

## 4 THERMAL-AWARE SCHEDULING

Computer chips like any other manufactured good have a temperature range within which they were designed to operate. When that range is exceeded the materials are stressed beyond their tolerance point and can melt, break, burn, or otherwise stop working resulting in a partial or complete failure of the chip. Such situations are called catastrophic failures and modern processors have technologies built into them, like AMD's Multi-Point Thermal Control or Intel's Adaptive Thermal Monitor, to avoid these occurrences. These failure-avoiding techniques can be broadly described as reactive thermal management. The processor is designed to handle the heat produced by a "typical workload"; however, certain workloads can more aggressively use the processor resources generating more heat than can be dissipated, leading to dangerous overheating. These situations are detected via temperature probes strategically located within the chip and when the temperature exceeds a manufacturer-predetermined threshold the thermal management techniques are activated. Thermal management techniques can lower the frequency and voltage of the processor, apply clock gating (duty cycles) to the processor, or halt it altogether. This is done until the temperature falls back below the acceptable threshold, at which point normal operation is resumed. Because these techniques are activated only once a temperature-critical situation has been reached and because they do nothing to prevent reaching such situations, they are classified as reactive techniques.

The nature of reactive thermal-management techniques that lower temperature by reducing processor capabilities has the potential, if active for long durations, to have a significantly adverse effect on thread performance. Much research has been done on *proactive* thermal management that takes preventative measures, which themselves have minimal or no performance impact, ensuring that critical temperatures that would trigger costly hardware reactions are never reached. Proactive thermal management relies on the old adage "a stitch in time saves nine".

Thermal crises leading to component failure are the most dramatic but not the only examples motivating the need for thermal management. Temperature gradients can be created in both space and time; they will stress the underlying materials and dramatically decrease the expected lifespan of the device [46]. Temperature gradients in space arise because different threads heat the processor differently. A thread that is very computebound will heat the processor by constantly issuing instructions, much more than a memory-bound thread, which will be stalled for most of its execution time. If such different threads are scheduled on adjacent cores then the resulting temperature gradient will be harmful to the chip's long-term durability. Similarly, if a core is frequently switched between hot and cold threads then the resulting temporal temperature gradient will

not be good for the components either. Proactive thermal management takes these effects into account as it tries to avoid hot spots and temperature gradients, by distributing the temperature as evenly across the chip as possible. Furthermore, temperature is directly proportional to leakage current, and so techniques that minimize the overall temperature are highly beneficial in terms of energy/power savings as well.

In this section the proactive techniques are further broken down into *static techniques* that determine the scheduling solution prior to the start of execution, and *dynamic techniques* that work throughout the execution of the workload to make improvements. Dynamic techniques are further divided into those that use temperature measurements directly available from on-chip sensors and those that construct thermal models to predict future temperature data in order to make policy decisions. We conclude the section with a discussion of how different thermal management strategies can be integrated in order to provide more robust solutions.

### 4.1 Static Thermal Management

One subset of proactive thermal-aware scheduling algorithms relies on static scheduling to meet predefined thermal goals. The static scheduling problem is best described by breaking an application into tasks, where each task is a function or a set of functions. The entire application is then represented as a Directed Acyclic Graph (DAG) of computation with the vertices representing the tasks and the directed edges representing the precedence relationships between the tasks. The problem becomes scheduling these tasks to the available cores such that the timing constraints for the tasks are met, the precedence constraints are met, as well as some thermal goal, such as keeping the max temperature below a particular threshold, is also met. Since the scheduling decisions are made once prior to the start of the run rather than dynamically during execution, these solutions are called static. Different types of algorithmic solutions have been proposed to tackle this problem.

Zhang et al. [47] derive an optimal solution to the static thermal-aware scheduling problem. They show that the problem of choosing a frequency at which to run each task as well as choosing the length of the low-power period for the processor in-between tasks such that the predefined temperature threshold is not exceeded and that the entire workload completes as quickly as possible is NP-hard. They show a *dynamic programming* (DP) optimal solution that runs in pseudo-polynomial time and an approximate fully polynomial time solution to this problem. Coskun et al. [48] use integer linear programming (ILP) to find scheduling solutions (mappings of tasks to cores as well as choosing each task's frequency/voltage setting) such that one of the following four metrics is optimized: the minimization of hot-spots (where one core or portion thereof significantly exceeds average chip temperatures), the minimization of

hot spots and thermal gradients (where there is a large temperature discrepancy between on chip resources), balancing energy load across the cores, or minimizing the total energy consumed.

Chantem et al. [49] use mixed integer linear programming (MILP) to decide on a mapping of tasks to a floorplan of cores as well as an ordering of tasks on each core such that all precedence and timing constraints are met while the preset max temperature is not exceeded. It is a well established fact that the rate at which cores cool depends on their location within the floorplan of the die. If cores are near edges they can more easily dissipate heat via those edges than cores which are in the middle of the chip. Chantem et al. use the cores' positions within the floorplan as part of its thermal-aware solution [49].

#### 4.2 Non-Predictive Proactive Thermal Management

The next subset of thermal-aware scheduling solutions that we consider are dynamic: they are active throughout the execution of the workload. These solutions are proactive since they attempt to facilitate favorable thermal conditions in the future. They are non-predictive in a sense that they rely on temperature measurements/estimations of the current chip state and do not create thermal models to forecast future temperatures.

Although modern chips come equipped with thermal sensors that can be read by software, these readings are subject to noise and other reliability issues; furthermore, the sensors are limited to only certain locations within the chip [50]. As such, preprocessing temperature readings prior to utilizing them in any scheduler can increase its accuracy and effectiveness. Sharifi et al. [50] propose a scheme to make online temperature measurements significantly more accurate. Offline they construct a thermal equivalent RC (Resistor-Capacitor) model for the circuit and reduce its complexity to make the model manageable. They apply Kalman filtering calibrated with sensor readings until a steady state is reached. The model is then usable online to convert the unreliable sensor data into reliable thermal readings.

Choi et. al [51] propose a set of hot-spot mitigation techniques incorporated into the OS scheduler and evaluate the effectiveness of these techniques on an IBM Power 5 processor. The foundation of their proposals lies on two observations: (1) functional units' power and temperature profiles are tightly related to per-unit utilization, in view of advanced fine-grained clock gating technologies incorporated into modern processors, and (2) because the OS is already performing thread scheduling with a time granularity much smaller than riseand fall-times on-chip temperatures, thermal mitigation techniques can be implemented at the OS level with low overhead. Their experimental evaluation shows that due to advanced clock gating in their target processor, exploiting the temporal and spatial heat slack when making scheduling decisions has a significant effect on the processor's temperature.

One of the key tools in proactive thermal management is the movement of threads from one core to another; usually from a hot core to a colder core. However, if migration of threads is explicitly disallowed, the throttling strategy proposed by Rajan and Yu [52] is mathematically proven to maximize throughput while maintaining the core temperature below the predefined threshold. The strategy throttles the core via DVFS to a precalculated level if the threshold temperature is reached. When the temperature falls below the threshold, the core is throttled back up to some maximum level that will not exceed the threshold. This is shown to be optimal for maximizing throughput over any other strategy so long as migration is disallowed. Stavrou and Trancoso[53] propose thermal-aware scheduling techniques that, although not explicitly restricting migration, focus on assigning newly dispatched threads onto cores rather than moving threads between cores. They propose scheduling techniques that assign the newly spawned thread to the coolest core on the chip. A more sophisticated version looks not only at the temperature of individual cores but also at the temperature of cores in the *neighborhood* around each core as well as the floorplan position of the core and computes a simple thermal goodness metric for each core. Further sophistication is added to this method by restricting scheduling to cores that exceed a predefined temperature threshold.

Coskun et al. [54] compare scheduling policies very similar to those proposed in [53] (e.g., mainly sending ready threads to the coolest core and sending ready threads to a core which "lives in the coolest neighborhood") against a more sophisticated technique called Adaptive Random. Adaptive Random assigns a probability of sending a thread to a core based on that core's past thermal history. A sliding window approach is used to keep track of the core's thermal history. At the end of each measuring period, the core's probability of receiving a thread is incremented if its temperature never exceeded a predefined threshold and decremented otherwise. The destination core for a thread is decided by generating a random number and determining the core to whose id that random number corresponds. The core's probability value as maintained via the sliding window method directly determines its likelihood of being the recipient of the thread. Thus cores with a better thermal history (those that spent more time below the threshold temperature) are more likely to be assigned threads.

Almost ubiquitously, thermal management algorithms try to ensure that the core is heated as little as possible while still performing an acceptable amount of work. Gomaa et al. [55] propose a strategy which is radically unique in that it actually seeks to more aggressively heat the cores. Although initially such an idea may seem counterintuitive there is a beautiful logic behind it: the authors argue that whether only one component of the core becomes overheated or ten components become overheated, the time for the core to cool will be roughly the same whether regardless of the number of overheated components. However, the workload that heated ten components within the core rather than only one most likely got significantly more work done and yet suffered the same cooling penalty as the less efficient workload. Gomaa put this radical theory into practice using a hyper-threading enabled CMP [55]. The proposed algorithm has two parts Heat and Run Thread Assignment (HRTA) and Heat and Run Thread Migration (HRTM). HRTA is responsible for pairing threads onto the same core with complementary resource demands such that they will heat different components within the core. The authors attempt to pair threads based on two main criteria: integer with floating point, and high IPC with low IPC. If thread pairings based on these broad criteria are not available then HRTA looks at more specific resource usage such as the cache and the ALU. They also seek to balance the IPC evenly across all cores to lengthen the times between cooling periods. Once a core has reached its threshold temperature, HRTM is responsible for migrating threads away from the overheated cores created by HRTA, allowing them to cool. It should be noted that the scheme proposed in [55] works only if the number of threads is smaller than the number of thread contexts available in the CMP, since HRTM relies on the existence of cooler, not overloaded, cores to migrate threads from the hot overloaded cores.

The work by Zhou et al. [56] analyzes thermal management issues on 3D processors, which consist of several vertically-stacked dies coupled with a dense, highspeed interface. Recent research has shown that 3D die stacking is an exciting new technology that increases transistor density and, at the same time, enables a significant reduction of interconnect both within a die and across dies in a system [57], [58]. In spite of these benefits, 3D die stacking gives rise to an increased power density per unit volume. A novel scheduling algorithm is proposed by Zhou et al. [56] to address this issue by taking into account the thermal conduction in the vertical direction. Based on the observation that a core in one layer could become hot because of a high power task running on the same vertical column but a different layer, the proposed scheduler performs thread-to-core assignments for sets of cores that are vertically aligned (super cores) rather than based on the temperatures of individual cores. Their experimental evaluation reveals that this scheduling technique significantly reduces the number of thermal crises and, so, it delivers better performance than conventional techniques designed for 2D processors. Furthermore, the authors argue that hardware techniques aimed to dramatically reduce a core's temperature upon a thermal emergency must be engaged in a per-core-stack fashion, and more specifically must be targeted to the core that contributes more significantly to increasing the temperature in this stack.

## 4.3 Predictive Proactive Thermal Management

This next subset of thermal-aware scheduling techniques is similar in both goals and strategies to the previous

11

subset except that instead of relying on temperature measurements from on-chip thermal sensors to drive decisions these management techniques incorporate sophisticated models to predict future core temperatures. The downside of this approach is that it adds significant complexity for the implementation both in terms of the code needed and the calculation time. The upside is that the scheduler becomes significantly more powerful being able to anticipate thermal crises as well as take actions that not only mitigate problems observed at the moment, but also reduce the probability of future crises.

Work by Yeo et al. [59] is a perfect example of how temperature predicting models can extend the thermalaware policies described earlier. The authors create a two-phase prediction model on the observation that the rate of change of temperature for an application is proportional to the difference between its current temperature and its steady state temperature (the temperature that it would acquire if running in a continuous loop). The two phases correspond to the *Application Based* Thermal Model (ABTM) and the Core Based Thermal Model (CBTM). The ABTM predicts the thread's future temperature using a recursive least squares method while CBTM relies on a simple differential equation, the core's initial temperature, the application's steady state temperature, and the observation above to predict the core's future temperature. The overall predicted future temperature for the thread running on the core is computed as a weighted sum of the predicted thread and predicted core temperatures. The obtained predicted temperatures are then used to perform thermal management. More concretely, if the predicted temperature of a certain thread-core-combination exceeds the defined threshold then that thread will be migrated to what is predicted to be the coolest core. It is easy to see how there is a clear advantage in performing such a migration without having to actually reach the threshold temperature.

A much more involved technique called Autoregressive Moving Average (ARMA) is used by Coskun et al. [60], [61], [62] to predict future temperatures. Under the assumption that temperature follows a stable distribution with a fixed mean and variance the authors model variations in temperature as a stochastic process. Offline they fit the collected data to a progressively higher order model until the error falls below a specified threshold thus obtaining the model parameters and residuals. The model residuals are checked for randomness ensuring no autocorrelation. An online adaptation is used to ensure that the model still describes the current workload. Workload changes are detected by applying a sequential probability ratio test (SPRT), i.e. statistical hypothesis testing on the distribution of model residuals. The model is adjusted on the fly to compensate for workload changes. The ARMA model allows thread temperatures to be forecast into the future. The authors explore using the predicted thread temperatures in several thermal-aware scheduling algorithms. Proactive-Migration moves threads away from cores that

are predicted to become excessively hot. Proactive-DVFS reduces the frequency/voltage of a core if its temperature is predicted to exceed a certain threshold. Finally, *Proactive-Thread Balance* (PTB) uses the ARMA results to migrate threads between the run queues of different cores to even out the temperature across the chip.

Although ARMA has been shown to be effective its complexity makes it an unattractive option for an online implementation. Azoub and Rosing [63] propose a more cost-effective prediction model based on the band limited nature of the temperature frequency spectrum. The proposed *Band-Limited Predictor* (BLP) requires no training phase and is able to accurately predict future events based on past events for a band limited signal (one which takes values only from a known range). The prediction results from this model are used in a similar fashion to those of other models mainly to migrate threads from cores predicted to be cold. The model is also used to allocate newly spawned threads to cores predicted to be cold.

Kumar et al [64] propose a thermal model that differs from the others in this section in that it does not seek to predict the future temperature of threads but rather to separate the temperature contributions made by the different threads time-sharing the same core. The approach relies on observing how much each thread uses various processor resources and correlating that to a temperature metric for those resources. More specifically, for each of the threads 22 performance metrics are dynamically collected online corresponding to the activity of different microarchitectural components of the processor. Offline partial least squares regression analysis is used to generate the coefficients necessary to convert the performance counter values into temperate values. The model is periodically, in a limited way, adjusted online during execution. The model is used to dynamically predict the temperature of individual threads on the core. If a thread's predicted temperature exceeds a predefined threshold then the proactive software module will use the priority mechanism available inside the Linux OS to limit the amount of time that that thread runs on the core. The size of the time slices allocated by Linux to a particular thread when multiplexing a processor between different threads depends on the priority level of that thread. The smaller the priority the longer the time slice. By decreasing the priority of "hot" threads the authors ensure that they run less, lowering the overall temperature of the core. In the method proposed in [64], if the proactive adjustment of thread priorities does not prevent overall core temperature from surpassing the predefined threshold then a reactive hardware technique is triggered, which cools the core by clock modulation.

By means of a comprehensive experimental analysis, the work by Yang et al. [65] showcases two limitations of Kumar's approach [64]. First, given that hot jobs are executed less frequently than cool jobs, cool jobs typically finish earlier than hot jobs. Putting off the execution of hot jobs may lead to a high number of thermal emergencies when the cool jobs are exhausted, thus causing a significantly adverse effect on performance. Second, Kumar's scheduler is inherently unfair since it tends to allocate less CPU time to hot jobs and more to cool jobs. In [65], a scheduling algorithm that is not subject to these limitations is presented. The algorithm follows the strategy of keeping the temperature right below the threshold but without exceeding it, based on the observation that this approach increases the heat removal rate and is less likely to incur thermal emergencies. As the next task to run this scheduler selects the hottest program that does not increase the temperature above the threshold; if such job does not exist, the hottest job is selected to run. The authors derive an elaborated estimation model that makes it possible for the scheduler to accurately predict the future temperature that results from running a particular job in the next time interval.

## 4.4 Integrating Multiple Thermal-Management Techniques

In this section we discussed a wide variety of thermalaware scheduling techniques covering the available literature on the subject. Each technique was, under certain circumstances, shown to be effective. Significant evidence has also been presented showing why thermal management is a vitally important issue for contemporary and future CMPs. The question that may logically arise is which method is better and should be adopted in operating systems by default? However, such a question is not the right one to ask. These methods are not mutually exclusive choices. There are positives and negatives about each method. There are situations and workloads where some methods work well and others fail and different circumstances where the roles are reversed. A promising direction is to combine several thermal management techniques, combining their strengths.

Some exciting work has already been done in the direction of multi-method thermal management. The work by Kumar et al. [64], described earlier, uses a proactive software technique to reduce the time "hot" threads spend on the processor but also uses a reactive clock modulation approach to guard against situations where the first method is insufficient. By default all modern processors are equipped with hardware based thermal crisis avoidance techniques like the Adaptive Thermal Monitor in Intel's Core i7 chips [24]. Thus any implemented thermal management technique is also safeguarded in hardware. Coskun et. al[66] demonstrate how a static thermal management technique first described in [48] can be combined with the Adaptive Random dynamic thermal-management technique introduced in [54] to improve overall efficiency.

Coskun et. al propose a framework in [67] for combining a variety of thermal management techniques and choosing the most appropriate one for the given workload. They reduce the problem of choosing a thermalmanagement technique to the *switching experts problem*. The experts are thermal-management policies. The expert to use during any given period is decided by a specialist based on a set of rules the specialist has and the currently measured load on the system. The specialist to use during any given period is decided using an online learning method that evaluates the specialists based on their performance or would-be performance in the past. The experts considered in [67] were: (1) the default OS scheduler, (2) DPM, which turns off idle cores after a fixed timeout, (3) DVFS+DPM, which scales the frequency of cores based on their utilization level and turns off idle cores, (4) migration, which moves threads from hot cores to colder ones, and (5) Adaptive Random [54]. The two specialists considered were utility based and temperature based each of which supports a subset of experts and decides which expert to use depending on the total system load.

Donald and Martonosi [68] provide a comprehensive study of how different thermal management policies can be used together. They divide the field into three orthogonal axes. The first axis describes if the policy uses stop-go (clock modulation) or DVFS. The second axis describes if the policy is applied globally to the CMP as a whole or to each core individually. The third axis describes if a migration policy is used and if so whether it is based on performance counters or thermal sensors. All possible permutations of these thermal-management policies are explored and a matrix showing the throughput achieved without exceeding a temperature threshold is derived. A major conclusion of that study was the value of DVFS which showed a 2.5X speedup in throughput over stop-go on average.

## 4.5 Summary

Even the most complex computer chip can still be thought of as an expensive resistor since it converts electric current that passes through it into heat. Excessive heat can damage the chip and turn it into an actual resistor. To prevent this, modern hardware is equipped with built-in thermal crisis prevention technologies that detect that the temperature has gone above an acceptable threshold and reactively halt or throttle the hardware until the temperature falls below this threshold. Although effective at avoiding complete melt-downs this reactive technology has the potential to impede performance and does nothing to prevent intra-chip thermal gradients, which can significantly limit the expected lifetime of these components. Proactive thermal-management performed by the OS scheduler can address thermal crises before they happen minimizing performance effects as well as addressing issues like thermal gradients. If the workload is known *a priori* it is possible to perform static thermal scheduling. The workload is broken into tasks, with dependencies among them captured in a graph. A schedule is then created by deciding on which tasks will run on which cores, when and to what degree each of the cores will be throttled, such that performance is optimized while avoiding any negative thermal effects. Since

it is typically not the case that the workload is known *a priori* less efficient but far more realistic dynamic proactive-thermal-aware scheduling becomes necessary. Using filtered or otherwise pre-processed readings from temperature probes located on the chip, often in conjunction with other data, such as the floorplan of cores or thread-performance counters the scheduler decides on thread-to-core mappings and core throttling to deliver peak performance without negative thermal effects. Further effectiveness but also complexity can be added to dynamic thermal-aware scheduling by constructing thermal models to predict future core temperatures and using these take truly proactive actions.

## 5 SCHEDULING FOR ASYMMETRIC SYSTEMS

An asymmetric multicore system is defined to include several cores that expose the same instruction-set architecture (ISA), but offer different performance, occupy different size on chip areas and have different power characteristics. Systems may be built asymmetric by design [69] – we refer to these as *explicitly asymmetric* - or asymmetry may arise as a result of non-uniform frequency scaling on different cores, or if variations in fabrication process prevent all cores from running at the same speed [70]. Explicitly asymmetric systems are also referred to as single-ISA heterogeneous systems. There is also another type of heterogeneous systems, where cores expose different ISA: for example the IBM Cell processor has one PPE (a general-purpose core) and a number of SPEs (special-purpose vector processing units). These systems require primarily compiler support, because code must be explicitly compiled to run on a particular core type. As a result, scheduling for these systems has not been an active area of research, at least at the time of this writing. Instead, we focus on asymmetric systems with a uniform ISA. On these systems, a thread scheduler is essential for maximizing system efficiency.

In explicitly asymmetric systems cores differ in microarchitecture. There is typically a small number of fast and powerful cores with complex microarchitectural features (super-scalar out-of-order pipeline, aggressive pre-fetching and branch prediction hardware, high clock speed), as well as a large number of slower and low power cores. The latter are characterized by simpler pipelines, slower clock frequencies, smaller areas, and lower power consumption as compared to the fast cores. The motivation for this architecture is superior performance per watt that can be achieved if the microarchitecture of a core is tailored to the workload. The idea is that fast cores are better suited for (1) workloads with high instruction-level parallelism (ILP) that effectively utilize the fast cores' advanced features, and (2) sequential applications or sequential phases of parallel applications. High-ILP workloads, to which we refer as CPU-intensive following the terminology adopted in earlier studies, achieve a greater speedup on fast cores relative to slow cores, because they utilize fast cores effectively. Low-ILP

workloads, to which we refer as *memory-intensive*, waste resources of the fast cores and typically achieve a better performance/watt when running on the slower cores. Scalable parallel applications can get good performance on slow cores, because they are able to spread the computation across them, while sequential or modestly-parallel applications need to run on fast cores to get good performance. We refer to this notion of preferring certain types of cores for certain types of computation as *specialization*. To deliver specialization the system must match each instruction stream with the type of core best suited to this stream. This process is typically a part of thread assignment or scheduling. Therefore, it is typical to provide specialization by means of *asymmetry-aware thread schedulers*.

An asymmetry-aware scheduler would assign threads to cores so as to deliver specialization: threads that benefit most from fast cores would be preferentially assigned to run on fast cores, while other threads would be relegated to slow cores. Note that most schedulers for explicitly asymmetric systems assume cores of two types: fast and slow. Kumar et al. [69] showed that having only two core types is sufficient to deliver the projected benefits of asymmetric systems.

The remainder of this section is organized as follows. Sections 5.1 and 5.2 survey different scheduling algorithms aimed to optimize the overall system efficiency on AMPs for workloads consisting of single-threaded and multithreaded applications, respectively. Section 5.3 is devoted to exploring schedulers that exploit less conventional types of specialization (i.e.: not directly related to the workload's ILP and parallelism). Section 5.4 focuses on asymmetry-aware schedulers pursuing goals other than optimizing for the overall system performance, such as fairness. Finally, Section 5.5 introduces another category of schedulers targeting AMPs where asymmetry was introduced as a result of variation in the fabrication process.

#### 5.1 Addressing single-threaded applications

The biggest challenge in designing an asymmetry-aware scheduler for multi-application workloads consisting of single-threaded applications is to determine to what degree the throughput of individual processes (or threads) will improve when running on a fast core relative to a slow core. Throughput is usually measured in terms of instructions per second (IPS), and the relative improvement is often referred to as the speedup factor or relative speedup. Schedulers proposed by Kumar et al. [71] and Becchi and Crowley [72] used the most natural and straightforward approach for determining relative speedup. These schedulers simply ran each thread on each type of core and measured its IPS in both cases. Once IPS on both core types was known, the scheduler computed the ratio of fast-core IPS to slow-core IPS. Threads with a higher ratio would be then assigned to run on fast cores and threads with a lower ratio

would be assigned to slow cores. (Kumar also proposed another algorithm based on sampling of entire thread assignments – we will discuss this algorithm later.)

While this approach was intuitive and simple, it did not work well in practice. The problem was rooted in phase changes. If a thread changes its phase during the period when the scheduler performs a measurement of its IPS on fast and slow cores, the resulting IPS ratio may be estimated incorrectly. Suppose, for instance, that a thread had a naturally high IPS while it was running on a fast core, for example because it was in a CPU-intensive phase. Then, when it was moved to a slow core it entered a very memory-intensive phase and so its IPS dropped. The scheduler would register a very high IPS on the fast core and a very low IPS on the slow core. The resulting IPS ratio would be high, signaling the scheduler that the thread should be assigned to the fast core. In reality though, the thread has entered a memory-bound phase and so assigning it to a fast core is counterproductive. (As we mentioned earlier, memory-bound threads use fast cores inefficiently, because they frequently stall the pipeline and make poor use of the advanced microarchitectural features.) Another problem with this algorithm was that scarce fast cores were in much higher demand than slow cores, because the scheduler often needed to re-measure the IPS of one thread or another on a fast core. This led to load imbalance and hurt performance.